由于能小縮減輸出電容器和感應器尺寸從而節省板空間,具有更快轉換頻率的直流-直流(DC/DC)轉換器正變得越來越受歡迎。而另一方面,由于處理器內核電壓降至1V以下,任務周期縮短了,在更快頻率下很難獲得低電壓,使得負載點電源的需求不斷增加。

很多電源IC供應商都在積極地推銷號稱能節省空間的更快的DC/DC轉換器。一個DC/DC轉換器能夠以1MH在甚至2MHz的頻率轉換,這聽起來似乎很不錯,但是在考慮電源系統的時候,不能光看到尺寸和效率。下面我們來看幾個例子,這幾個例子都顯示了轉換頻率更高時的優點和缺點。

選擇一個應用

我們設計并構建了三種不同電源來展示高速轉換頻率的利弊。這三種電源的輸入電壓都是5V,輸出電壓都是1.8V,輸出電流3A。這是DSP、ASIC和FPGA等性能處理器的通用要求。為了限定濾波器設計和性能,允許的波紋電壓設在20mV,大約是輸出電壓的1%;峰至峰感應器電流設為1A。

我們來對比一下這三種頻率分別為的350, 700和1600 kHz的電源的利弊。三種方案都使用頻率1.6 MHz、低電壓、帶MOSFET的TPS54317型3 A同步降壓DC/DC轉換器作為調壓器。

選擇感應器和電容器

感應器和電容器都是依照下面的簡單公式來選擇的:

Equation 1:

V = L x di/dt

Rearranging: L ≥ Vout x (1-D)/(ΔI x Fs)

where: ΔI = 1 A peak-to-peak; D = 1.8 V/5 V=0.36

等式1:

V = L x di/dt

Rearranging: L ≥ Vout x (1-D)/(ΔI x Fs)

此處 ΔI = 1 A峰至峰; D = 1.8 V/5 V=0.36

等式2:

I = C x dv/dt

Rearranging: C ≥ 2 x ΔI/(8 x Fs x ΔV)

此處 ΔV = 20 mV, I = 1 A 峰至峰

等式2中假定使用了一個有可忽略串聯電阻的電容器-陶瓷電容器即是如此。由于它的低電阻和小尺寸,三種方案都選用了陶瓷電容器。上面等式2中2的乘數是隨DC偏置出現的電容降,因為這一影響沒有算在大多數陶瓷電容器的數據表內。

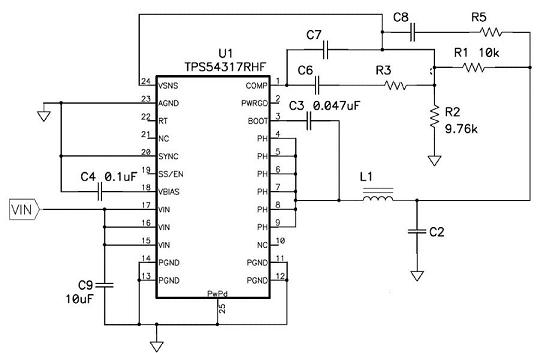

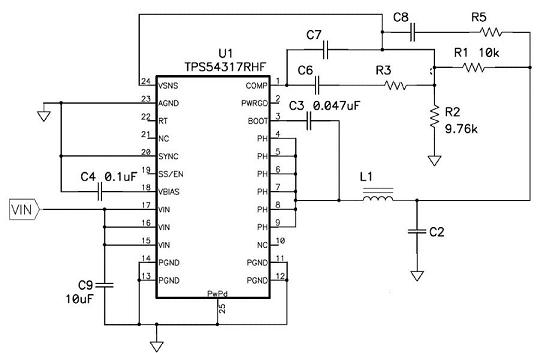

圖1的電路用來評估測試臺上每個方案的性能

|

|

圖1:TPS54317參考示意圖

|

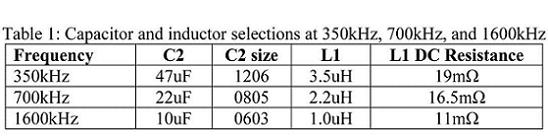

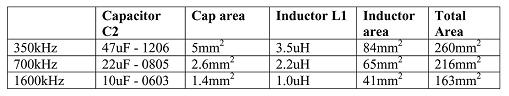

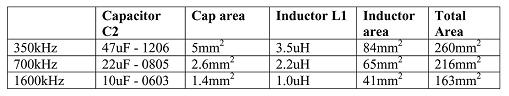

在示意圖中沒有數值的元件就是在各個方案中被更改的元件。輸出濾波器由L1和C2組成。三種方案中所有這些元件的數值都在表格1中列出,并根據上面等式結果來選擇。

|

|

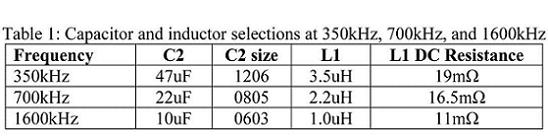

表格1:頻率分別為350kHz, 700kHz,和1600 kHz時的電容器和感應器選項

|

必須注意,隨著頻率的增加,每個感應器的DC電阻會減小。這是因為圈數越少所需的銅線長度就越小。誤差放大器補償元件則根據每個轉換頻率而單獨設計。本文暫不討論如何選擇補償數值。

最小啟動時間

數字轉換器-數字轉換器集成電路(IC)在最小可控制啟動時間上有限值,即脈寬調制(PWM)電路可獲得的最窄脈寬。在降壓轉換器中,場效應晶體管(FET)在一個轉換周期內處于開啟狀態的時間比成為任務周期,等于輸出電壓和輸入電壓之比。

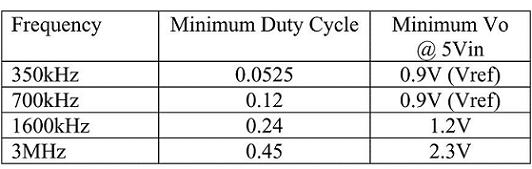

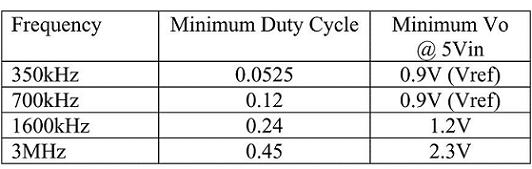

上面例子中的TPS54317型轉換器任務周期為0.36 (1.8V/5.0V),最小啟動時間為數據表中所示的150ns(最大值)。可控制脈寬的限制產生了可獲得的最小任務周期,根據等式3可以很容易算出來。一旦知道了最小任務周期,就可以計算出最低可獲取輸出電壓,如等式4和表格2中所示。最低輸出電壓也受到轉換器參考電壓限制,TPS54317的最低輸出電壓為0.9V。

等式3:

最小任務周期=最小啟動時間x 轉換頻率

等式4:

最低輸出電壓=輸入電壓x 最小任務周期(受TPS54317參考電壓限制)

|

|

表格2:最小啟動時間為150ns時的最低輸出電壓

|

此處可以在1.6MHz轉換頻率的情況下產生1.8V的輸出電壓。但是,即便頻率是3MH在,最可能低的輸出電壓也會被限制在2.3V。還有個方法就是降低輸入電壓或者降低頻率。在選擇轉換頻率之前,最好檢查一下DC/DC轉換器數據表,以確保一個最小可控制啟動時間。

脈沖跳躍

如果DC/DC轉換器不能以足夠快的速度消除柵極脈沖以保持所需的任務周期,就會產生脈沖跳躍。電源會試著調節輸出電壓,但是波紋電壓會隨著脈沖的進一步分離而增大。由于脈沖跳躍的原因,輸出波紋會顯示出分諧波成分,由此可能產生噪音。而由于IC可能不會對一個大的電流尖峰作出反應,也有可能電流限制電路不能繼續正常工作。有時由于控制器沒有正常工作,控制回路可能也會不穩定。最小可控制啟動時間是一個很重要的因素,因此最好要核對DC/DC轉換器數據表中的規格,以確認獲得最好的頻率和最小啟動時間組合。

效率和功率消耗

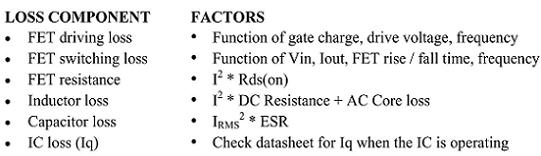

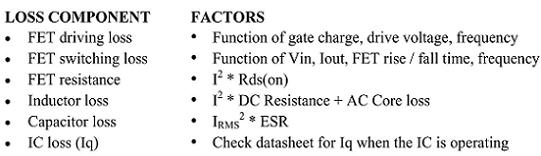

在設計電源時,DC/DC 轉換器的效率是需要考慮的最重要因素之一。如果效率太差,就會導致高功率消耗,需要在電路板上借助散熱器或者PCB上更多的銅線才能處理好。功率消耗也會需要更多的電源上行。功率消耗有下面幾個成分:

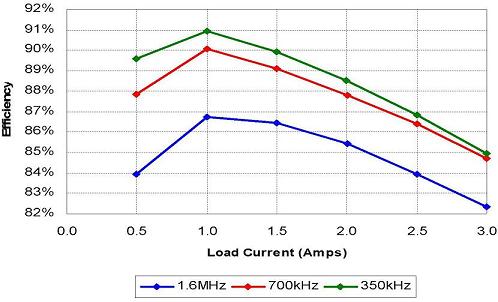

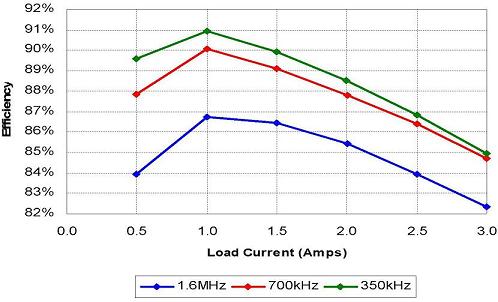

這里的三個方案的損耗來自FET驅動損耗、FET轉換損耗和感應器損耗。FET電阻和IC損耗是一樣的,因為三個方案使用同樣的IC。由于每個方案都使用了陶瓷電容器,電容器損耗可以忽略不計,因為它們的等效串行電阻很低。為了顯示高頻率轉換的效果,圖2對每個方案的效率進行了測量和闡述。

這里的三個方案的損耗來自FET驅動損耗、FET轉換損耗和感應器損耗。FET電阻和IC損耗是一樣的,因為三個方案使用同樣的IC。由于每個方案都使用了陶瓷電容器,電容器損耗可以忽略不計,因為它們的等效串行電阻很低。為了顯示高頻率轉換的效果,圖2對每個方案的效率進行了測量和闡述。

|

|

圖2:輸入電壓5V輸出電壓1.8V時不同頻率的不同效率

|

上圖清晰地顯示出效率隨著轉換頻率的增加而降低。為了能在任何頻率情況下都改進效率,需要一個具有低Rds (on)、閘電壓或全負載時靜止電流規格的DC/DC轉換器,或者等效電阻更低的電容器和感應器。

大小

表格3顯示了感應器和電容器的數值,以及PCB所需板面面積

|

|

表格3:元件大小和總面積要求

|

電容器或感應器的推薦板面面積是比單個元件稍大一些,以上三個方案都要將板面面積大小計算在內。然后,總面積的大小就是將各個元件所占面積相加,包括IC和濾波器的板面面積,以及所有其它小的電阻器和電容器乘以2,以作為元件間隔。從350 kHz 到1600 kHz能節省的面積很大,濾波器大小可以減少50%,板空間減少35%,節省了將近100 mm2。

但由于電容值和電感值不能降為零,必定會符合回報消減規律。換句話說,提高頻率不能無限制地降低總體面積,因為適當尺寸的批量生產的感應器和電容器是有限定范圍的。

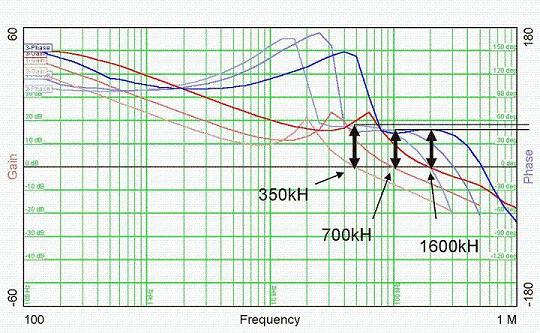

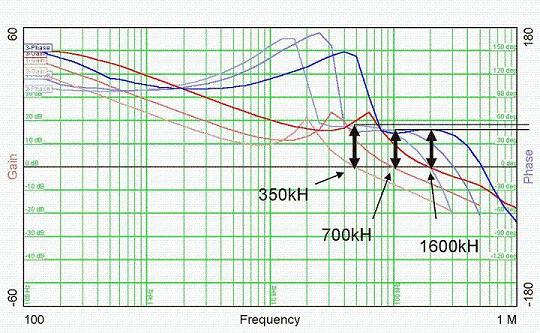

瞬間反應

瞬間反應是衡量電源性能等級的一個很好的指標。我們利用每個電源的在更高轉換頻率下的波德圖來進行對比。如圖3所示,每個電源的相位補角都在45度到55度之間,這是一個抑制效果不錯的瞬間反應。

|

|

圖3:批量為350 kHz, 700 kHz和1600 kHz.時的波德圖

|

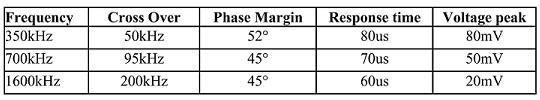

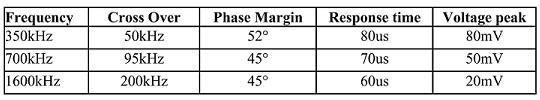

交越頻率大約是轉換頻率的1/8。當使用一個快速轉換的DC/DC轉換器時,要確保電源IC誤差放大器有足夠的帶寬來支持一個高交越頻率。TPS54317的誤差放大器單位增益帶寬一般是5MHz。表格4顯示了實際瞬間反應次數和相關電壓峰值過沖值。

|

|

表格4:瞬間反應

|

轉換頻率越高就帶寬越大,過沖值就越低。低瞬間電壓過沖對于一些新的性能處理器是必須的,因為它們的調節精度要求可能包括瞬時電壓峰值是3%。

當需要更高的輸出電流時,德州儀器的TPS40140型可堆疊、雙通道并使用外部MOSFET的1 MHz DC/DC控制器可以滿足要求。快速轉換頻率的優勢可以通過交叉多個功率階段并將之從相位中轉換出去來實現。

例如,可以將四個頻率分別為500kHz的輸出堆在一起,就行成了2MHz的有效頻率。這樣作的好處是可以減少波紋,降低輸入塊電容,加快瞬間反應,并通過在電路板上擴散功率消耗來改進熱量管理。最多可以將8個TPS40140通過數字總線連在一起并實現相位同步,最大有效頻率高達16MHz。

總結

設計轉換器時要進行利弊權衡。更小的面積、更快的瞬間反應和更小的電壓過沖和下沖是本文談到的“利”,而功率的降低和散熱的增加則是“弊”。

如果突破了極限,可能會產生一些問題,比如脈沖跳躍和噪音。在為高頻率應用選擇DC/DC轉換器時,要核查制造商的數據表,以確認一些重要的規格,例如最小啟動時間、誤差放大器的增益帶寬、FET電阻和轉換損耗等。在這些規格上有良好性能的集成電路可能成本會更高,但卻物有所值,而且在遇到設計難題時更容易使用。

評論列表

我要評論